#### **General Comments**

The paper deals with a comparison of non-accelerated and accelerated air quality simulations, using Intel CPUs, Nvidia GPUs, and unspecified Chinese hardware. The topic is well suited and is overall interesting and relevant. Nonetheless, there are in my opinion major issues with the manuscript which limit its broader interest. I summarise my overall impression and critique here, and also attach an annotated pdf.

**Response:** We appreciate the referee for reviewing our manuscript and for the valuable suggestions, which we will address point by point in the following and improve our revised manuscript according the comments and suggestions in the pdf.

Q1: A first major issue in the paper is that the Chinese hardware remains unknown for the readers throughout the text. Very little information about this hardware is disclosed, which makes it very difficult to assess and understand potentially relevant differences. The reader might infer/guess some parts of this (e.g., that CUDA cannot be used to program the Chinese accelerators), but these properties of the hardware are not mentioned. The reason for the lack of information is also not disclosed. In comparison of course, one can find full technical specifications for the Intel and Nvidia hardware used in the study. We are not explained why these Chinese accelerator are GPU-like and not quite GPUs. We are also provided very little information on the Chinese CPUs. This creates, in my opinion quite some intransparency.

Response: Thanks for the constructive comment. Sorry we didn't give more information about the domestic GPUs and domestic CPUs in the paper, and in the revised manuscript we will try our best to improve those information as we can. It maybe that due to the U. S. ban on the sale of some advanced chips to China, and the manufacturers are not willing to release the full technical specifications, so we cannot directly obtain the full information about the GPUs and CPUs. In order to provide the readers with more detailed information, we tried our best to query the software environment and hardware configuration of the clusters by remote access, and listed them in lines 122-143 of the manuscript, hoping to be helpful to readers. In addition, we reply to the issue that CUDA cannot be used to program on domestic GPUs as follows. At present, the Radeon Open Compute platform (ROCm) toolkit developed by AMD can be used to program the domestic GPU. ROCm is an open-source software platform for HPC and hyperscale GPU computing (ROCm, 2023). On the ROCm software platform, it uses the AMD's HIP interface which is a C++ runtime API to allows developers to run programs on AMD GPUs and Chinese GPU-like accelerators.

**Lines 122-143:** Table 1 listed four GPU clusters which are conducted the experiments, two NVIDIA heterogeneous clusters which have the same hardware configuration as Cao et al. (2023) and two China's domestically heterogeneous clusters newly used in this research, namely "Songshan"

supercomputer and "Taiyuan" computing platform. Two NVIDIA heterogeneous clusters are equipped with NVIDIA Tesla K40m and V100 GPU accelerators, respectively. Both two domestic clusters include thousands of computing nodes and each containing one China's domestically CPU processor, four China's domestically GPU-like accelerators, and 128 GB of DDR4 2666 memory. The domestic CPU has four NUMA nodes, each NUMA node has eight X86 based processors. The accelerator adopts a GPU-like architecture consisting of a 16 GB HBM2 device memory and many compute units. The GPU-like accelerators connected to CPU with PCI-E, the peak bandwidth of the data transfer between main memory and device memory is 16 GB/s.

It is worth noting that the "Taiyuan" computing platform, which has been updated in three main aspects compared to the "Songshan" supercomputer. The CPU clock speed has been increased from 2.0 GHz to 2.5 GHz, the number of GPU-like computing units has been increased from 3,840 to 8,192, and the peak bandwidth between main memory and video memory has been increased from 16 GB/s to 32 GB/s. In addition, the NVIDA GPU is programmed using the CUDA toolkit, and the domestic GPU-like is programmed using the ROCm-HIP toolkit developed by AMD in 2015 for HPC and hyperscale GPU computing (ROCm, 2023). On the ROCm software platform, it uses the AMD's HIP interface to allows developers to run programs on Chinese GPU-like accelerators. More details about the hardware composition and software environment of the four heterogeneous clusters are presented in Table 1.

Table 1. Configurations of the NVIDIA K40m cluster, NVIDIA V100 cluster, "Songshan" supercomputer, and "Taiyuan" computing platform.

|                            | Hardware components                                    |                                                                                 |

|----------------------------|--------------------------------------------------------|---------------------------------------------------------------------------------|

|                            | CPU                                                    | GPU                                                                             |

| NVIDIA K40m cluster        | Intel Xeon E5-2682 v4 CPU<br>@2.5 GHz, 16 cores        | NVIDIA Tesla K40m GPU, 2880 CUDA cores, 12 GB video memory                      |

| NVIDIA V100 cluster        | Intel Xeon Platinum 8168 CPU<br>@2.7 GHz, 24 cores     | NVIDIA Tesla V100 GPU, 5120 CUDA cores, 16 GB video memory                      |

| Songshan supercomputer     | China's domestically CPU processor A, 2.0GHz, 32 cores | China's domestically GPU-like accelerator A, 3840 computing units, 16 GB memory |

| Taiyuan computing platform | China's domestically CPU processor B, 2.5GHz, 32 cores | China's domestically GPU-like accelerator B, 8192 computing units, 16 GB memory |

|                            | Software environment                                   |                                                                                 |

|                            | Compiler and MPI                                       | Programming model                                                               |

| NVIDIA K40m cluster        | Intel Toolkit 2021.4.0                                 | CUDA-10.2                                                                       |

| NVIDIA V100 cluster        | Intel Toolkit 2019.1.144                               | CUDA-10.0                                                                       |

| Songshan supercomputer     | Intel Toolkit 2021.3.0                                 | ROCm-4.0.1/DTK-23.04                                                            |

| Taiyuan computing platform | Intel Toolkit 2021.3.0                                 | DTK-23.04                                                                       |

relative to that obtained with the Chinese accelerators (larger errors for Nvidia hardware, which the authors attribute to the fact that Nvidia favours performance over accuracy!). To sustain such claims not only is more evidence required, but also significant information on the hardware and the software stack over which the application is built.

**Response:** Thanks for the constructive comment. In this manuscript, by comparing the simulation results of different versions of CAMx model, it can be seen that GPU-HADVPPM4HIP has less deviation on domestic GPU-like accelerators. Because the simulation accuracy of geoscience numerical model is closely related to the model efficiency, and many model optimization works improve the computational performance by reducing the precision of the data, such as Váňa et al. (2017) changed some variables precision in the atmospheric model from double precision to single precision, which increased the overall computational efficiency by 40%, and Wang et al. (2019) improved the computational efficiency of the gas-phase chemistry module in the air quality mode by 25%~28% by modifying the floating-point precision compile flag. Therefore, we speculate that this may be related to the manufacturing process of NVIDIA GPUs and domestic GPU-like accelerators, especially NIVIDA Tesla V100 series GPUs, which may use unknown optimizations to improve GPU performance efficiency by losing part of the accuracy. In this study, we mainly focus on numerical simulation. Of course, we also want to know the specific reasons for this, but we are not professional GPU research and development designers, and do not know the underlying design logic of the hardware, so we can only present our experimental results in the air pollution model to the readers, and discuss with each other to jointly promote the application of GPU in the field of geoscience numerical models. We have added this discussion in lines 282-298, which are as follows:

Lines 282-298: From AEs, REs, and ratio of RMSE and std between different CAMx versions, it is less difference that the GPU-HADVPPM4HIP program runs on the "Songshan" supercomputer. Because the simulation accuracy of geoscience numerical model is closely related to the model efficiency, and many model optimization works improve the computational performance by reducing the precision of the data, such as Váňa et al. (2017) changed some variables precision in the atmospheric model from double precision to single precision, which increased the overall computational efficiency by 40%, and Wang et al. (2019) improved the computational efficiency of the gas-phase chemistry module in the air quality mode by 25%-28% by modifying the floatingpoint precision compile flag. Therefore, we speculate that this may be related to the manufacturing process of NVIDIA GPUs and domestic GPU-like accelerators, especially NIVIDA Tesla V100 series GPUs, which may use unknown optimizations to improve GPU performance efficiency by losing part of the accuracy. In this study, we mainly focus on numerical simulation. Of course, we also want to know the specific reasons for this, but we are not professional GPU research and development designers, and do not know the underlying design logic of the hardware, so we can only present our experimental results in the air pollution model to you, and discuss with each other to jointly promote the application of GPU in the field of geoscience numerical models.

**Q3:** My second point is that the manuscript is a bit confusing in terms of which processes are mapped to which hardware. This may be simply a matter of clarification, in particular when it comes to the in-node heterogeneous processes ("other modules" the authors state, are solved using OpenMP on the CPUs, whereas the advection module, when solved on CPUs is on a single core?). I would suggest a sketch to explain this.

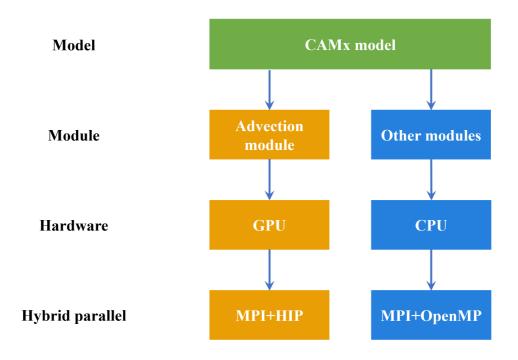

**Response:** Sorry for not being able to explain it clearly and thanks for the constructive comment. The original CAMx model supports message passing interface (MPI) parallel technology running on the general-purpose CPU. The simulation domain is divided into several sub-regions by MPI, and each CPU process is responsible for simulation of its sub-region, which includes advection module and other modules such as photolysis module, deposition module, chemical module, etc. In the previous study, Cao et al. (2023) adopt a parallel architecture with an MPI and CUDA (MPI+CUDA) hybrid paradigm to configure one GPU accelerator for each CPU process. For the advection module, the simulation originally implemented by the CPU is handed over to the GPU. Other module computing tasks continue to be completed on the CPU. In this study, in addition to the MPI+HIP hybrid parallel scheme to realize the advection module running on several domestic GPU-like accelerators, the OpenMP (OMP) hybrid parallel framework of CAMx model is further introduced to realize the MPI+OMP hybrid parallelism of other modules on CPU. A schematic of the multi-level hybrid parallel framework is shown in Figure 2. For example, in a computing node, four CPU processes and four GPU-like accelerators are launched, and each CPU process spawns four threads. Then the advection module is simulated by 4 GPU-like accelerators, and the other modules are done by 4\*4 threads spawned by CPU processes. We have modified this part in lines 179-191, which are as follows:

Lines 179-191: As mentioned above, the original CAMx model supports message passing interface (MPI) parallel technology running on the general-purpose CPU. The simulation domain is divided into several sub-regions by MPI, and each CPU process is responsible for simulation of its sub-region, which includes advection module and other modules such as photolysis module, deposition module, chemical module, etc. In the previous studying, Cao et al. (2023) adopt a parallel architecture with an MPI and CUDA (MPI+CUDA) hybrid paradigm to configure one GPU accelerator for each CPU process. For the advection module, the simulation originally implemented by the CPU is handed over to the GPU. Other module computing tasks continue to be completed on the CPU.

In this study, when the CUDA C code of GPU-HADVPPM is converted to HIP C code, GPU-HADVPPM with an MPI and HIP (MPI+HIP) heterogeneous hybrid programming technology can also run on multiple domestic GPU-like accelerators. The MPI and HIP hybrid parallel scheme can also configure one GPU-like accelerator for each CPU process. However, the number of GPU-like accelerators in a single compute node is usually much smaller than the number of CPU cores in the

heterogeneous HPC systems. Therefore, in order to make full use of the remaining CPU computing resources, the OpenMP (OMP) hybrid parallel framework of CAMx model is further introduced to realize the MPI+OMP hybrid parallelism of other modules on CPU. A schematic of the multi-level hybrid parallel framework is shown in Figure 2. For example, in a computing node, four CPU processes and four GPU-like accelerators are launched, and each CPU process spawns four threads. Then the advection module is simulated by 4 GPU-like accelerators, and the other modules are done by 4\*4 threads spawned by CPU processes.

Figure 2. A schematic of the multi-level hybrid parallel framework.

**Q4:** In terms of the results, the text needs to be much more specific on how the runs are computed and how the speed up is computed. One can infer that speed up is computed against runs on the Chinese CPU, but it is not fully clear if that is using a parallel run on all cores or on a serial job.

Response: Sorry for not being able to explain it clearly. According to the results of Cao et al. (2023), the parallel design of the CAMx model adopts the primary/secondary mode, and Process 0 (P0) is responsible for inputting and outputting the data and calling the MPI\_Barrier function to synchronize the process, and the other processes are responsible for simulation. When testing the computational performance of the advection module on the CPU, we only launch two CPU processes, namely P0 and Process 1 (P1), where P0 is mainly responsible for data input and output and synchronization process, and P1 is mainly responsible for simulation. In the P1 process, the system\_clock functions in the Fortran language are used to test the elapsed time of the advection module on the CPU. Similarly, when testing the computation performance of the advection module on the GPU-like accelerator, we only launch 2 CPU processes and 2 GPU-like accelerators. When

a P1 process runs to the advection module, the original computation process is migrated from the CPU to the GPU, and the hipEvent\_t function in HIP programming is used to test the running time of the advection module on the GPU-like accelerator. We have modified this part in lines 310-322, which are as follows:

Lines 310-322: According to the results of Cao et al. (2023), the parallel design of the CAMx model adopts the primary/secondary mode, and Process0 (P0) is responsible for inputting and outputting the data and calling the MPI\_Barrier function to synchronize the process, and the other processes are responsible for simulation. When testing the computational performance of the advection module on the CPU, we only launch two CPU processes, namely P0 and Process1 (P1), where P0 is responsible for data input and output and synchronization process, and P1 is mainly responsible for simulation. In the P1 process, the system\_clock functions in the Fortran language are used to test the elapsed time of the advection module on the CPU. Similarly, when testing the computation performance of the advection module on the GPU-like accelerator, we only launch 2 CPU processes and 2 GPU-like accelerators. When a P1 process runs to the advection module, the original computation process is migrated from the CPU to the GPU, and the hipEvent\_t function in HIP programming is used to test the running time of the advection module on the GPU-like accelerator.

**Q5:** The authors identify host-device transfers as the key bottleneck, mainly by computing the share of time spent on kernels and on data transfers. The authors seem to conclude that this can only be improved with better bandwidth between host and device. However, nothing is said about potential implementation issues (e.g., poor handling of memory allocations) or even bottlenecks which could be alleviated with better suited algorithms. Indeed, the fraction of time the solver actually spends on running GPU kernels is very low (below 24%) which is very inefficient.

Response: Sorry for not being able to explain it clearly. Data transfer between CPU and GPU is one of the main factors that limit the efficiency of geoscience numerical models in heterogeneous clusters (Mielikainen et al., 2012; Mielikainen et al., 2013; Huang et al., 2013). On the one hand, improving the data transfer bandwidth between CPU and GPU can improve the computational efficiency of the model in heterogeneous clusters. On the other hand, the optimization measures can be implemented to improve the data transfer efficiency between CPU and GPU. For example, (1) Asynchronous data transfer is used to reduce the communication latency between CPU and GPU. Computation and data transfer are performed simultaneously to hide communication overhead; (2) Currently, some advanced GPU architectures support a unified memory architecture, so that the CPU and GPU can share the same memory space and avoid frequent data transfers. This reduces the overhead of data transfer and improves data transfer efficiency; (3) Cao et al. (2023) adopted communication optimization measures to reduce the communication frequency in one time integration step to one, but there is still the problem of high communication frequency in the whole simulation. In the future, we will consider porting other hotspots of CAMx model, or even the whole

integral module except I/O, to GPU-like accelerators for increasing the proportion of code on the GPU and reduce the frequency of CPU-GPU communication. We have added this part in **lines 367-372**, which are as follows:

Lines 367-372: Data transfer between CPU and GPU is one of the main factors that limit the efficiency of geoscience numerical models in heterogeneous clusters (Mielikainen et al., 2012; Mielikainen et al., 2013; Huang et al., 2013). On the one hand, improving the data transfer bandwidth between CPU and GPU can improve the computational efficiency of the model in heterogeneous clusters. On the other hand, the optimization measures can be implemented to improve the data transfer efficiency between CPU and GPU. For example, (1) Asynchronous data transfer is used to reduce the communication latency between CPU and GPU. Computation and data transfer are performed simultaneously to hide communication overhead; (2) Currently, some advanced GPU architectures support a unified memory architecture, so that the CPU and GPU can share the same memory space and avoid frequent data transfers. This reduces the overhead of data transfer and improves data transfer efficiency; (3) Cao et al. (2023) adopted communication optimization measures to reduce the communication frequency in one time integration step to one, but there is still the problem of high communication frequency in the whole simulation. In the future, we will consider porting other hotspots of CAMx model, or even the whole integral module except I/O, to GPU-like accelerators for increasing the proportion of code on the GPU and reduce the frequency of CPU-GPU communication.

**Q6:** Going back to the accuracy aspect, the authors don't really provide an in-depth discussion of why there are differences between the different computations. The magnitude of the errors is way above arithmetic accuracy of the hardware involved, and the claims that Nvidia hardware favours performance over accuracy are not well supported by the exercise carried out in this manuscript. This requires much better defined benchmarks. Overall, the differences between the simulations could be due to a wide variety of reasons, anywhere from arithmetic accuracy of the hardware and the hardware-specific arithmetic kernels, sure, but all the way up to errors in the different implementations. The investigation is simply not deep enough to support the claims nor to provide robust evidence of the root causes of the differences. There is no discussion on why, for example, the different species show different variability in the errors, although this suggests that whatever the root cause of the error, this propagates differently across different processes/state variables.

**Response:** Thanks for the constructive comment. In the error analysis of this paper, the simulation results of CAMx model on a general CPU processor (Intel Xeon E5-2682 v4 CPU) are used as the benchmark to compare the deviation of simulation results on different GPUs. From the comparison results, GPU-HADVPPM4HIP has less deviation on domestic GPU-like accelerators. As mentioned above, because the simulation accuracy of geoscience numerical model is closely related to the model efficiency, and many model optimization works improve the computational performance by

reducing the precision of the data. Therefore, we speculate that this may be related to the manufacturing process of NVIDIA GPUs and domestic GPU-like accelerators, especially NIVIDA Tesla V100 series GPUs, which may use unknown optimizations to improve GPU performance efficiency by losing part of the accuracy. Since we are not GPU developers and do not know the underlying design logic of the hardware, so we can only present our experimental results for discussion. We have added this discussion in **lines 282-298**, which are as follows:

Lines 282-298: From AEs, REs, and ratio of RMSE and std between different CAMx versions, it is less difference that the GPU-HADVPPM4HIP program runs on the "Songshan" supercomputer. Because the simulation accuracy of geoscience numerical model is closely related to the model efficiency, and many model optimization works improve the computational performance by reducing the precision of the data, such as Váňa et al. (2017) changed some variables precision in the atmospheric model from double precision to single precision, which increased the overall computational efficiency by 40%, and Wang et al. (2019) improved the computational efficiency of the gas-phase chemistry module in the air quality mode by 25%-28% by modifying the floatingpoint precision compile flag. Therefore, we speculate that this may be related to the manufacturing process of NVIDIA GPUs and domestic GPU-like accelerators, especially NIVIDA Tesla V100 series GPUs, which may use unknown optimizations to improve GPU performance efficiency by losing part of the accuracy. In this study, we mainly focus on numerical simulation. Of course, we also want to know the specific reasons for this, but we are not professional GPU research and development designers after all and do not know the underlying design logic of the hardware, so we can only present our experimental results in the air pollution model to you, and discuss with each other to jointly promote the application of GPU in the field of geoscience numerical models.

## Below are responses to the comments and suggestions listed in the attached pdf file.

## Line 2:

domestic is always relative.

It is clear this refers to the Chinese hardware discussed in the paper. However, the term is found too often in the text and is not particularly useful.

Is there no name for the accelerator? In the text the authors can extend in explaining what this hardware is, including that it is developed in China.

**Response:** Thanks for the constructive comment. On the one hand, Chinese chip manufacturers are reluctant to release specific details of Chinese hardware, possibly due to the impact of the U. S. ban on the sale of advanced GPUs in China. On the other hand, according to Reviewer 1's suggestion, we have changed the title of this paper to: *GPU-HADVPPM4HIP V1.0: using the heterogeneous interface for portability (HIP) to speed up the piecewise parabolic method in the CAMx (v6.10) air*

quality model on China's domestic GPU-like accelerator.

## **Line 63:**

Strike out

**Response:** Sorry for this mistake. We have revised this part in **lines 64-65**, which are as follows:

**Lines 64-65**: In terms of the heterogeneous porting for air quality model, most scholars select the chemical module, one of the hotspots, to implement heterogeneous porting, and porting the computational process originally on the CPU processes to the GPU accelerator, in order to improve the computing efficiency.

### Line 64:

it is not quite clear what is meant here

**Response:** Sorry for not being able to explain it clearly. In terms of the heterogeneous porting for air quality model, most scholars select the chemical module, one of the hotspots, to implement heterogeneous porting, and porting the computational process originally on the CPU processes to the GPU accelerator, in order to improve the computing efficiency. We have modified this part as follows:

**Lines 64-65**: In terms of the heterogeneous porting for air quality model, most scholars select the chemical module, one of the hotspots, to implement heterogeneous porting, and porting the computational process originally on the CPU processes to the GPU accelerator, in order to improve the computing efficiency.

# **Line 66:**

compared to what?

Response: Sorry for not being able to explain it clearly. Sun et al. (2018) used CUDA technology to port the second-order Rosenbrock solver of chemistry module of CAM4-Chem to NVIDIA Tesla K20X GPU, and achieved up 11.7x speedup compared to the AMD Opteron<sup>TM</sup> 6274 (Interlagos) CPU (16 cores) using one CPU core. We have modified this part in lines 66-67, which are as follows:

**Lines 66-67**: Sun et al. (2018) used CUDA technology to port the second-order Rosenbrock solver of chemistry module of CAM4-Chem to NVIDIA Tesla K20X GPU, and achieved up 11.7x speedup compared to the AMD Opteron<sup>TM</sup> 6274 (Interlagos) CPU (16 cores) using one CPU core.

## **Line 73:**

compared to what?

**Response:** Sorry for not being able to explain it clearly. The KPPA-generated SAPRC'99 mechanism from CMAQ model achieved a maximum speedup of 13.7x and KPPA-generated RADM2 mechanism from WRF-chem model achieved an 8.5x speedup both compared to the Intel Quad-Core Xeon 5400 series CPU. We have modified this part in **lines 73-74**, which are as follows:

**Lines 73-74**: The KPPA-generated SAPRC'99 mechanism from CMAQ model achieved a maximum speedup of 13.7x and KPPA-generated RADM2 mechanism from WRF-chem model achieved an 8.5x speedup both compared to the Intel Quad-Core Xeon 5400 series CPU.

## **Line 76:**

Reduction

**Response:** Sorry for this mistake. We have revised this part in **lines 74-79**, which are as follows:

**Lines 74-79:** Similarly, the advection module is also one of the hotspot modules in the air quality model, Cao et al. (2023) adopted the Fortran-C-CUDA C scheme and implemented a series of optimizations, including reduction the CPU–GPU communication frequency, optimize the GPU memory access, and thread and block co-indexing, to increase the computational efficiency of the HADVPPM advection solver. It can achieve up to the 18.8x speedup on the NVIDIA Tesla V100 GPU compared to the Intel Xeon Platinum 8168 CPU.

### **Line 75:**

this clause here is hanging. I guess you intend to say something like "Conernign horizontal advection modules for atmospheric chemical models, Cao..."

**Response:** Sorry for not being able to explain it clearly. Similarly, the advection module is also one of the hotspot modules in the air quality model, Cao et al. (2023) adopted the Fortran-C-CUDA C scheme and implemented a series of optimizations, including reduction the CPU–GPU communication frequency, optimize the GPU memory access, and thread and block co-indexing, to increase the computational efficiency of the HADVPPM advection solver. It can achieve up to the 18.8x speedup on the NVIDIA Tesla V100 GPU compared to the Intel Xeon Platinum 8168 CPU. We have revised this part in **lines 74-79**, which are as follows:

**Lines 74-79:** Similarly, the advection module is also one of the hotspot modules in the air quality model, Cao et al. (2023) adopted the Fortran-C-CUDA C scheme and implemented a series of optimizations, including reduction the CPU–GPU communication frequency, optimize the GPU memory access, and thread and block co-indexing, to increase the computational efficiency of the

HADVPPM advection solver. It can achieve up to the 18.8x speedup on the NVIDIA Tesla V100 GPU compared to the Intel Xeon Platinum 8168 CPU.

**Line 78:**

compared to what?

**Response:** Sorry for not being able to explain it clearly. Similarly, the advection module is also one of the hotspot modules in the air quality model, Cao et al. (2023) adopted the Fortran-C-CUDA C scheme and implemented a series of optimizations, including reduction the CPU–GPU communication frequency, optimize the GPU memory access, and thread and block co-indexing, to increase the computational efficiency of the HADVPPM advection solver. It can achieve up to the 18.8x speedup on the NVIDIA Tesla V100 GPU compared to the Intel Xeon Platinum 8168 CPU. We have revised this part in **lines 74-79**, which are as follows:

**Lines 74-79:** Similarly, the advection module is also one of the hotspot modules in the air quality model, Cao et al. (2023) adopted the Fortran-C-CUDA C scheme and implemented a series of optimizations, including reduction the CPU–GPU communication frequency, optimize the GPU memory access, and thread and block co-indexing, to increase the computational efficiency of the HADVPPM advection solver. It can achieve up to the 18.8x speedup on the NVIDIA Tesla V100 GPU compared to the Intel Xeon Platinum 8168 CPU.

**Line 81:**

Highlight

**Response:** Sorry for this mistake. We have revised this part in **lines 81-82**, which are as follows:

**Lines 81-82:** The CUDA technology was implemented to carry out heterogeneous porting for the atmospheric chemical models from the CPU processors to different NVIDIA GPU accelerators.

**Line 85:**

The Fortran

**Response:** Sorry for this mistake. We have revised this part in **lines 85-87**, which are as follows:

**Lines 85-87:** First, we compared the simulation result of the Fortran version CAMx model with the CAMx-CUDA and CAMx-HIP model which were coupled with the CUDA and HIP versions of GPU-HADVPPM program, respectively.

**Line 85:**

The CUDA

**Response:** Sorry for this mistake. We have revised this part in **lines 85-87**, which are as follows:

**Lines 85-87:** First, we compared the simulation result of the Fortran version CAMx model with the CUDA version of CAMx (CAMx-CUDA) and CAMx-HIP model which were coupled with the CUDA and HIP versions of GPU-HADVPPM program, respectively.

**Line 84:**

why is this a GPU-like accelerator and not simply "accelerator" or simply a GPU?

**Response:** Sorry for not being able to explain it clearly. In the previous study, we implement the NVIDIA GPU to accelerate the advection module in the CAMx model (Cao et al.,2023). In this study, the domestic GPU-like accelerator plays the same role as the NVIDIA GPU, which is also used to accelerate the advection module. As mentioned above, Chinese chip manufactures are reluctant to disclose the specific details of the GPU, probably due to the US ban on selling advanced GPUs to China, so we don't know the detailed architecture and can only refer to it as a GPU-like accelerator. We have added this part in **lines 81-84**, which are as follows:

**Lines 81-84:** In this study, the Heterogeneous-computing Interface for Portability (HIP) interface was introduced to implement the porting of GPU-HADVPPM from the NVIDIA GPU to the China's domestically GPU-like accelerators based on the research of Cao et al. (2023). The domestic GPU-like accelerator plays the same role as the NVIDIA GPU, which is also used to accelerate the advection module in the CAMx model, so we refer to it as a GPU-like accelerator.

**Line 86:**

the CUDA and HIP versions

**Response:** Sorry for this mistake. We have revised this part as follows:

**Lines 85-87:** First, we compared the simulation result of the Fortran version CAMx model with the CAMx-CUDA and CAMx-HIP model which were coupled with the CUDA and HIP versions of GPU-HADVPPM program, respectively.

**Line 88:**

Were

**Response:** Sorry for this mistake. We have revised this part in **lines 87-88**, which are as follows:

Lines 87-88: And then, the computing performance of GPU-HADVPPM programs on different

GPUs were compared.

### Line 89:

does this system have a name?

**Response:** Thanks for the constructive comment. In this paper, domestic heterogeneous cluster A refers to the "Songshan" supercomputer from the Henan Province, and domestic heterogeneous cluster B refers to the Taiyuan computing platform from the Shanxi Province. We have changed the names of all heterogeneous clusters accordingly.

## Line 105:

this statement warrants a supporting reference

**Response:** Thanks for the constructive comment. We have added a supporting reference **lines 104-105**, which are as follows:

**Lines 104-105:** The PPM horizontal advection scheme (HADVPPM) was selected in this study because it provides higher accuracy with minimal numerical diffusion (ENVIRON, 2014).

## Line 106:

Schemes

**Response:** Sorry for this mistake. We have revised it as follows:

**Lines 105-106:** The other numerical schemes selected during the CAMx model testing are listed in *Table S1*.

## Line 106:

do you maybe mean "testing" here?

**Response:** Sorry for not being able to explain it clearly. We have revised this part in **lines 105-106**, which are as follows:

**Lines 105-106:** The other numerical schemes selected during the CAMx model testing are listed in Table S1.

## **Line 116:**

Strikeout

**Response:** Sorry for this mistake. We have revised this part in **lines 114-115**, which are as follows:

**Lines 114-115**: CUDA is a proprietary application programming interface (API) and as such is only supported on NVIDIA's GPUs.

## Line 123:

Allowing

**Response:** Sorry for this mistake. We have revised this part in **lines 122-124**, which are as follows:

**Lines 122-124**: On the ROCm software platform, it uses the AMD's HIP interface which is a C++ runtime API allowing developers to run programs on AMD GPUs.

## Line 124:

illustrates, or shows examples of the differences?

**Response:** Sorry for not being able to explain it clearly. We have revised this part in **lines 124-125**, which are as follows:

**Lines 124-125:** Table 1 shows examples of the differences between the CUDA programming and HIP programming on the NVIDIA GPU and AMD GPU.

## Line 126:

they are very similar

**Response:** Sorry for this mistake. We have revised this part in lines 125-127, which are as follows:

**Lines 125-127:** In general, they are very similar and their code can be converted directly by replacing the string "cuda" with "hip" in the most cases.

## Line 126:

String

**Response:** Sorry for this mistake. We have revised this part in **lines 125-127**, which are as follows:

Lines 125-127: In general, they are very similar and their code can be converted directly by replacing the string "cuda" with "hip" in the most cases.

## Line 126:

Is

**Response:** Sorry for this mistake. We have revised this part in lines 127-128, which are as follows:

**Lines 127-128:** *More information about HIP API is available on the AMD ROCm website (ROCm, 2023).*

### Line 130:

does this GPU-like accelerator have a name?

**Response:** Sorry for not being able to explain it clearly. As mentioned above, Chinese chip manufactures are reluctant to disclose the specific details of the GPU, probably due to the US ban on selling advanced GPUs to China, so we don't know the name of this GPU-like accelerator either.

# Line 129:

Presumably it is not possible to run CUDA code on the Chinese accelerators. Please state so explicitly.

As I'm sure it is clear for the authors, the lack of details of the accelerators implies readers are unaware of the software required to program this hardware.

**Response:** Sorry for not being able to explain it clearly. The CUDA code cannot run directly on domestic GPU-like accelerators, and it needs to be transcoded into HIP code. As mentioned above, Chinese chip manufactures are reluctant to disclose the specific details of the GPU, probably due to the US ban on selling advanced GPUs to China, so we don't more specific information, and all the information we know as well as are listed in Table 2. We have revised this part in **lines 127-128**, which are as follows:

**Lines 127-128:** Similar to AMD GPU, developers can also use ROCM-HIP programming interface to implement programs running on the China's domestically GPU-like accelerator. The CUDA code cannot run directly on domestic GPU-like accelerators, and it needs to be transcoded into HIP code.

## Line 135:

Lists

**Response:** Sorry for this mistake. We have revised this part in **lines 135-137**, which are as follows:

**Lines 135-137:** Table 2 lists four GPU clusters where we conducted the experiments, two NVIDIA heterogeneous clusters which have the same hardware configuration as Cao et al. (2023) and two China's domestically heterogeneous clusters newly used in this research, namely "Songshan" supercomputer and "Taiyuan" computing platform.

## Line 135:

Where we

**Response:** Sorry for this mistake. We have revised this part in **lines 135-137**, which are as follows:

**Lines 135-137:** Table 2 lists four GPU clusters where we conducted the experiments, two NVIDIA heterogeneous clusters which have the same hardware configuration as Cao et al. (2023) and two China's domestically heterogeneous clusters newly used in this research, namely "Songshan" supercomputer and "Taiyuan" computing platform.

## Line 147:

Units

**Response:** Sorry for this mistake. We have revised this part in **lines 147-148**, which are as follows:

**Lines 147-148:** The GPU-like accelerator A has 64 compute units, and each of the compute units can compute up to 60 parallel threads.

#### Line 147:

not sure "totaling" means here... does it mean each of the 64 units can compute up to 60 parallel threads?

**Response:** Sorry for not being able to explain it clearly. We have revised this part in **lines 147-148**, which are as follows:

**Lines 147-148:** The GPU-like accelerator A has 64 compute units, and each of the compute units can compute up to 60 parallel threads.

### Line 147:

In general, providing names for the clusters, the CPUs and the accelerators would improve readability and would be more informative for the readers.

Some references to additional technical specifications of the CPUs and accelerators would also be very welcome.

**Response:** Sorry for not being able to explain it clearly. In this paper, domestic heterogeneous cluster A refers to the "Songshan" supercomputer from the Henan Province, and domestic heterogeneous cluster B refers to the Taiyuan computing platform from the Shanxi Province. We have changed the names of all heterogeneous clusters accordingly. As mentioned above, Chinese chip manufactures are reluctant to disclose the specific details of the GPU, probably due to the US ban on selling advanced GPUs to China, so we don't more specific information, and all the

information we know as well as are listed in Table 1.

### Line 155:

In terms

**Response:** Sorry for this mistake. We have revised this part in **lines 155-157**, which are as follows:

**Lines 155-157:** In terms of the software environment, the Intel Toolkit (including compiler and MPI library) version 2021.4.0, 2019.1.144, and 2021.3.0 are employed for compiling on Intel CPU and China's domestically series CPU, respectively.

## Line 173:

Strikeout

**Response:** Sorry for this mistake. We have revised this part in **lines 173-175**, which are as follows:

**Lines 173-175:** Then the CUDA and HIP technology were used to convert the standard C code into CUDA C and HIP C code to make it computable on the NIVIDA GPU and domestic GPU-like accelerator.

### Line 176:

Strikeout

**Response:** Sorry for this mistake. We have revised this part in **lines 176-178**, which are as follows:

**Lines 176-178:** In this study, the ROCm HIP technology was used to implement the operation of GPU-HADVPPM on domestic GPU-like accelerator based on the CUDA version of GPU-HADVPPM which was developed by Cao et al. (2023).

## Line 179:

Strikeout

**Response:** Sorry for this mistake. We have revised this part in **lines 178-180**, which are as follows:

**Lines 178-180:** The HIP code was compiled using the "hipcc" compiler driver with the library flag "-lamdhip64".

## Line 192:

what exactly does this mean?

**Response:** Sorry for not being able to explain it clearly. We have revised this part in **lines 191-192**, which are as follows:

**Lines 191-192:** In the process of CAMx simulation, using MPI+OMP hybrid parallelism, several CPU processes can be launched, and each process can spawn several threads. This hybrid parallelism can significantly improve the computational efficiency of CAMx model.

#### Line 193:

Strikeout

**Response:** Sorry for this mistake. We have revised this part in lines 193-195, which are as follows:

**Lines 193-195:** In the previous study, Cao et al. (2023) adopt a parallel architecture with an MPI and CUDA (MPI+CUDA) hybrid paradigm to expand the parallel scale of CAMx-CUDA model in NVIDIA heterogeneous cluster:

#### Line 208:

Are reported

**Response:** Sorry for this mistake. We have revised this part in **lines 207-208**, which are as follows:

**Lines 207-208:** The coupling performance experiments of CUDA and HIP version GPU-HADVPPM are reported in this section.

### Line 208:

The

**Response:** Sorry for this mistake. We have revised this part in **lines 208-210**, which are as follows:

**Lines 208-210:** First, we compared the simulation result of the Fortran version CAMx model with CAMx-CUDA and CAMx-HIP model which were coupled with CUDA and HIP version of GPU-HADVPPM program, respectively.

## Lines 203-205:

perhaps it would be useful to provide a sketch of how the different types of processes map to hardware, both with and without the OpenMP for the "other modules".

**Response:** Sorry for not being able to explain it clearly and thanks for the constructive comment. The original CAMx model supports message passing interface (MPI) parallel technology running on the general-purpose CPU. The simulation domain is divided into several sub-regions by MPI,

and each CPU process is responsible for simulation of its sub-region, which includes advection module and other modules such as photolysis module, deposition module, chemical module, etc. In the previous studying, Cao et al. (2023) adopt a parallel architecture with an MPI and CUDA (MPI+CUDA) hybrid paradigm to configure one GPU accelerator for each CPU process. For the advection module, the simulation originally implemented by the CPU is handed over to the GPU. Other module computing tasks continue to be completed on the CPU. In this study, in addition to the MPI+HIP hybrid parallel scheme to realize the advection module running on several domestic GPU-like accelerators, the OpenMP (OMP) hybrid parallel framework of CAMx model is further introduced to realize the MPI+OMP hybrid parallelism of other modules on CPU. A schematic of the multi-level hybrid parallel framework is shown in Figure 2. For example, in a computing node, four CPU processes and four GPU-like accelerators are launched, and each CPU process spawns four threads. Then the advection module is simulated by 4 GPU-like accelerators, and the other modules are done by 4\*4 threads spawned by CPU processes. We have modified this part in lines 179-191, which are as follows:

Lines 179-191: As mentioned above, the original CAMx model supports message passing interface (MPI) parallel technology running on the general-purpose CPU. The simulation domain is divided into several sub-regions by MPI, and each CPU process is responsible for simulation of its sub-region, which includes advection module and other modules such as photolysis module, deposition module, chemical module, etc. In the previous studying, Cao et al. (2023) adopt a parallel architecture with an MPI and CUDA (MPI+CUDA) hybrid paradigm to configure one GPU accelerator for each CPU process. For the advection module, the simulation originally implemented by the CPU is handed over to the GPU. Other module computing tasks continue to be completed on the CPU.

In this study, when the CUDA C code of GPU-HADVPPM is converted to HIP C code, GPU-HADVPPM with an MPI and HIP (MPI+HIP) heterogeneous hybrid programming technology can also run on multiple domestic GPU-like accelerators. The MPI and HIP hybrid parallel scheme can also configure one GPU-like accelerator for each CPU process. However, the number of GPU-like accelerators in a single compute node is usually much smaller than the number of CPU cores in the heterogeneous HPC systems. Therefore, in order to make full use of the remaining CPU computing resources, the OpenMP (OMP) hybrid parallel framework of CAMx model is further introduced to realize the MPI+OMP hybrid parallelism of other modules on CPU. A schematic of the multi-level hybrid parallel framework is shown in Figure 2. For example, in a computing node, four CPU processes and four GPU-like accelerators are launched, and each CPU process spawns four threads. Then the advection module is simulated by 4 GPU-like accelerators, and the other modules are done by 4\*4 threads spawned by CPU processes.

Figure 2. A schematic of the multi-level hybrid parallel framework.

#### Lines 216-224:

presumably these test cases have been used already in previous studies. Please refer to them for completeness.

**Response:** Sorry for not being able to explain it clearly. In the previous study of Cao et al. (2023), we only used BJ case to carry out the performance test, HN case and ZY case are the newly constructed test cases in this study, so we think it is necessary to introduce the experimental setup of the three test cases in detail. We have revised this part in **lines 216-224**, which are as follows:

Lines 216-224: There are three test cases were used to evaluate the coupling performance of CUDA and HIP version GPU-HADVPPM. The experimental setup for the three test cases is shown in Table 2. In the previous study of Cao et al. (2023), we only used BJ case to carry out the performance test, HN case and ZY case are the newly constructed test cases in this study. The Beijing case (BJ) covers Beijing, Tianjin, and part of the Hebei Province with 145 × 157 grid boxes, and simulation of BJ case starts on 1 November, 2020. The Henan case (HN) mainly covers the Henan Province with 209 × 209 grid boxes. The starting date of simulation in HN case is 1 October, 2022. The Zhongyuan case (ZY) has the widest coverage of the three cases, with Henan Province as the center, covering the Beijing-Tianjin-Hebei region, Shanxi Province, Shaanxi Province, Hubei Province, Anhui Province, Jiangsu Province, and Shandong Province, with 531 × 513 grid boxes. ZY case started simulation on 4 January, 2023.

Line 236:

By the

**Response:** Sorry for this mistake. We have revised this part in lines 235-237, which are as follows:

**Lines 235-237:** The hourly concentrations of four major species, i.e.  $O_3$ ,  $PSO_4$ , CO, and  $NO_2$ , outputted by the Fortran, CUDA, and HIP versions of CAMx for the BJ case are compared to verify the results correctness before testing the computational performance.

Line 236:

Versions

**Response:** Sorry for this mistake. We have revised this part in **lines 235-237**, which are as follows:

**Lines 235-237:** The hourly concentrations of four major species, i.e. O3, PSO4, CO, and NO2, outputted by the Fortran, CUDA, and HIP versions of CAMx for the BJ case are compared to verify the results correctness before testing the computational performance.

Line 237:

Correctness

**Response:** Sorry for this mistake. We have revised this part in lines 235-237, which are as follows:

**Lines 235-237:** The hourly concentrations of four major species, i.e. O3, PSO4, CO, and NO2, outputted by the Fortran, CUDA, and HIP versions of CAMx for the BJ case are compared to verify the results correctness before testing the computational performance.

Line 237:

Computational

**Response:** Sorry for this mistake. We have revised this part in **lines 235-237**, which are as follows:

**Lines 235-237:** The hourly concentrations of four major species, i.e. O3, PSO4, CO, and NO2, outputted by the Fortran, CUDA, and HIP versions of CAMx for the BJ case are compared to verify the results correctness before testing the computational performance.

Line 237:

Shows

**Response:** Sorry for this mistake. We have revised this part in **lines 237-240**, which are as follows:

**Lines 237-240:** Fig. 2 shows the four major species simulation results of the three CAMx version, including Fortran version on the Intel E5-2682 v4 CPU, CUDA version on the NVIDIA K40m cluster and HIP version on the "Songshan" supercomputer, after 48 hours integration, as well as the absolute errors (AEs) of their concentrations.

### Line 238:

The three

**Response:** Sorry for this mistake. We have revised this part in **lines 237-240**, which are as follows:

**Lines 237-240:** Fig. 2 shows the four major species simulation results of the three CAMx version, including Fortran version on the Intel E5-2682 v4 CPU, CUDA version on the NVIDIA K40m cluster and HIP version on the "Songshan" supercomputer, after 48 hours integration, as well as the absolute errors (AEs) of their concentrations.

## Line 240:

relative to the serial Fortran version? Please state this explicitly.

Response: Sorry for not being able to explain it clearly. According to the results of Cao et al. (2023), the parallel design of the CAMx model adopts the primary/secondary mode, and Process 0 (P0) is responsible for inputting and outputting the data and calling the MPI\_Barrier function to synchronize the process, and the other processes are responsible for simulation. When comparing the simulation results, we only launched 2 CPU processes on the CPU platform, and launched 2 CPU processes and configure 2 GPU accelerators on the NVIDIA K40m and "Songshan" supercomputer respectively. We have revised this part in lines 240-246, which are as follows:

**Lines 240-246:** As mentioned above, the parallel design of the CAMx model adopts the primary/secondary mode, and P0 process is responsible for inputting and outputting the data and calling the MPI\_Barrier function to synchronize the process, and the other processes are responsible for simulation. When comparing the simulation results, we only launched 2 CPU processes on the CPU platform, and launched 2 CPU processes and configure 2 GPU accelerators on the NVIDIA K40m and "Songshan" supercomputer respectively.

## Line 250:

Not being knowledgeable of how the solver is implemented, are the concentrations of the different species (in terms of ppbV and microgram/m3) the state variables solved? Or are they derived quantities?

The reason I ask is, assuming the algorithms are identical, the differences must then come from

arithmetic precision on the different implementations. One would hope to see errors for the state variables in the order of arithmetic precision of the hardware.

Please elaborate and discuss this.

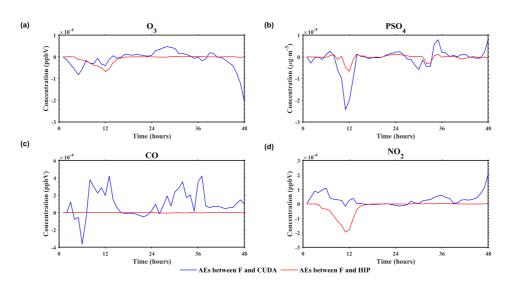

Response: Thanks for the constructive suggestion. Fig. 2 shows the four major species simulation results of the three CAMx version, including Fortran version on the Intel E5-2682 v4 CPU, CUDA version on the NVIDIA K40m cluster and HIP version on the "Songshan" supercomputer, after 48 hours integration, as well as the absolute errors (AEs) of their concentrations. In order to further explore the AEs accumulation and growth between the CUDA version and HIP version of CAMx model and the original Fortran version after heterogeneous porting, Figure 3 highlights the time series of AEs between Fortran and CUDA versions and between Fortran and HIP versions after grid averaging. As is shown in Figure 3, the AEs of O<sub>3</sub>, PSO<sub>4</sub>, CO, and NO<sub>2</sub> between the Fortran version and the CUDA version are -0.0002 to 0.0001 ppbV, -0.00003 to 0.00001  $\mu g \cdot m^{-3}$ , -0.0004 to 0.0004 ppbV, and -0.0002 to 0.0002 ppbV, respectively, and fluctuate. Although the AEs of the above four species between the Fortran and the HIP version also fluctuates, the fluctuation range is much smaller than that of the CUDA version. Importantly, the AEs between Fortran and CUDA versions and between Fortran and HIP versions both do not accumulate and grow over prolonged simulation periods. We have added this discussion in lines 248-255, which are as follows:

Lines 248-255: As is shown in Figure 3, the AEs of  $O_3$ ,  $PSO_4$ , CO, and  $NO_2$  between the Fortran version and the CUDA version are -0.0002 to 0.0001 ppbV, -0.00003 to 0.00001  $\mu g \cdot m^{-3}$ , -0.0004 to 0.0004 ppbV, and -0.0002 to 0.0002 ppbV, respectively, and fluctuate. Although the AEs of the above four species between the Fortran and the HIP version also fluctuates, the fluctuation range is much smaller than that of the CUDA version. Importantly, the AEs between Fortran and CUDA versions and between Fortran and HIP versions both do not accumulate and grow over prolonged simulation periods.

Figure 3. The time series of AEs between Fortran and CUDA versions (solid blue line) and between Fortran and HIP versions (solid red line) after grid averaging. Panel (a)~(d) represent the AEs of O<sub>3</sub>, PSO<sub>4</sub>, CO, and NO<sub>2</sub>,

## Line 265 Figure 3:

Is the far larger range of errors for PS04 explainable?

More generally, if the errors come from hardware-dependent arithmetic, how does this transfer to different ranges of error for the different species? What explains this?

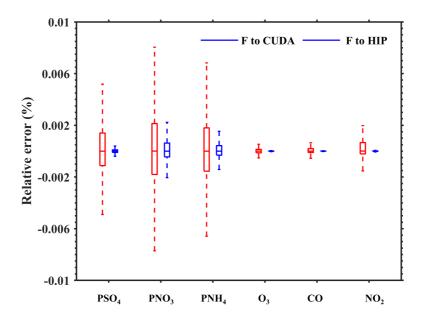

Response: Sorry for not being able to explain it clearly. PSO<sub>4</sub> is selected as the representative of secondary particulate matter. In the air quality model, the secondary particulate matter, such as PNH<sub>4</sub>, PNO<sub>3</sub>, and PSO<sub>4</sub>, have a common characteristic: their initial concentration is very low and they are mainly generated through complex chemical reactions. Therefore, when calculating the relative error on different hardware platforms, because the value in the denominator is very small, it is very sensitive to a small difference in the numerator, resulting in a large relative error. But from the absolute error in Fig.1, the absolute error of PSO<sub>4</sub> on different hardware platforms is smaller than that of other species. Fig. 3 presents the boxplot of the relative errors (REs) in all grid boxes for the PSO<sub>4</sub>, PNO<sub>3</sub>, PNH<sub>4</sub>, O<sub>3</sub>, CO, and NO<sub>2</sub> during the 48 hours simulation under the BJ case. As mentioned above, the initial concentration of secondary particles such as PSO<sub>4</sub>, PNO<sub>3</sub> and PNH<sub>4</sub> is very small. Therefore, when calculating the relative error, a small difference in the numerator leads to a large relative error value. For gaseous pollutants such as CO, O<sub>3</sub>, and NO<sub>2</sub>, the initial concentration is large due to emission, and the denominator value is large when calculating the relative error, which is insensitive to small differences in the numerator. We have revised this part in lines 257-263, which are as follows:

Lines 257-263: Fig. 3 presents the boxplot of the relative errors (REs) in all grid boxes for the PSO4, PNO3, PNH4, O3, CO, and NO2 during the 48 hours simulation under the BJ case. Statistically, the REs between the CUDA version on the NVIDIA K40m cluster and Fortran version on the Intel E5-2682 v4 CPU for the above six species are in the range of  $\pm 0.006\%$ ,  $\pm 0.01\%$ ,  $\pm 0.008\%$ ,  $\pm 0.002\%$ ,  $\pm 0.002\%$ , and  $\pm 0.002\%$ . In terms of REs between the HIP version on the "Songshan" supercomputer and Fortran version on the Intel E5-2682 v4 CPU, the values are much smaller than REs between CUDA and Fortran versions which are fall into the range of  $\pm 0.0005\%$ ,  $\pm 0.004\%$ ,  $\pm 0.004\%$ ,  $\pm 0.00006\%$ ,  $\pm 0.00004\%$ , and  $\pm 0.00008\%$ , respectively. In the air quality model, the secondary particulate matter, such as PNH4, PNO3, and PSO4, have a common characteristic: their initial concentration is very low and they are mainly generated through complex chemical reactions. Therefore, when calculating the relative error on different hardware platforms, because the value in the denominator is very small, it is very sensitive to a small difference in the numerator, resulting in a large relative error. But from the absolute error in Fig.1, the absolute error of PSO4 on different hardware platforms is smaller than that of other species. For gaseous pollutants such as CO, O3, and NO2, the initial concentration is large due to emission, and the denominator value is large when calculating the relative error, which is insensitive to small differences in the numerator.

Figure 3. The distribution of REs in all grid boxes for the PSO<sub>4</sub>, PNO<sub>3</sub>, PNH<sub>4</sub>, O<sub>3</sub>, CO, and NO<sub>2</sub> under the BJ case. The red boxplot represents the REs between the CUDA version on the NVIDIA K40m cluster and Fortran version on the Intel E5-2682 v4 CPU, and blue boxplot represents the REs between the HIP version on the "Songshan" supercomputer and Fortran version on the Intel E5-2682 v4 CPU.

# Line 288:

how can you support this claim? can you show this with simple kernels, or provide references for this?

**Response:** Sorry for not being able to explain it clearly. In this paper, by comparing the simulation results of different versions of CAMx, it can be seen that GPU-HADVPPM4HIP has less deviation on domestic GPU-like accelerators. Because the simulation accuracy of geoscience numerical model is closely related to the model efficiency, and many model optimization works improve the computational performance by reducing the precision of the data, such as Váňa et al. (2017) changed some variables precision in the atmospheric model from double precision to single precision, which increased the overall computational efficiency by 40%, and Wang et al. (2019) improved the computational efficiency of the gas-phase chemistry module in the air quality mode by 25%~28% by modifying the floating-point precision compile flag. Therefore, we speculate that this may be related to the manufacturing process of NVIDIA GPUs and domestic GPU-like accelerators, especially NIVIDA Tesla V100 series GPUs, which may use unknown optimizations to improve GPU performance efficiency by losing part of the accuracy. In this study, we mainly focus on numerical simulation, and the difference of hardware is not in the scope of our study. Of course, we also want to know the specific reasons for this, but we are not professional GPU research and development designers after all and do not know the underlying design logic of the hardware, so we can only present our experimental results in the air pollution model to you, and discuss with each

other to jointly promote the application of GPU in the field of geoscience numerical models. We have added this discussion in lines 282-298, which are as follows:

Lines 282-298: From AEs, REs, and ratio of RMSE and std between different CAMx versions, it is less difference that the GPU-HADVPPM4HIP program runs on the "Songshan" supercomputer. Because the simulation accuracy of geoscience numerical model is closely related to the model efficiency, and many model optimization works improve the computational performance by reducing the precision of the data, such as Váňa et al. (2017) changed some variables precision in the atmospheric model from double precision to single precision, which increased the overall computational efficiency by 40%, and Wang et al. (2019) improved the computational efficiency of the gas-phase chemistry module in the air quality mode by 25%-28% by modifying the floatingpoint precision compile flag. Therefore, we speculate that this may be related to the manufacturing process of NVIDIA GPUs and domestic GPU-like accelerators, especially NIVIDA Tesla V100 series GPUs, which may use unknown optimizations to improve GPU performance efficiency by losing part of the accuracy. In this study, we mainly focus on numerical simulation, and the difference of hardware is not in the scope of our study. Of course, we also want to know the specific reasons for this, but we are not professional GPU research and development designers after all and do not know the underlying design logic of the hardware, so we can only present our experimental results in the air pollution model to you, and discuss with each other to jointly promote the application of GPU in the field of geoscience numerical models.

#### Line 296:

I'm not sure what you meant here

**Response:** Sorry for not being able to explain it clearly. We have revised this part in **lines 295-296**, which are as follows:

**Lines 295-296:** As described in Sect. 4.2, we validate the 48 hours simulation results outputted by the Fortran, CUDA, and HIP versions of CAMx.

## Lines 297-301:

the syntax here is wrong.

I think you mean something like this:

Next, the computational performance were compared for the Fortran version...., the CUDA version. .... and the HIP version...., under the BJ, HN and ZY case.

It is unclear to me here what "coupling" is intended to mean.

**Response:** Sorry for not being able to explain it clearly. We have revised this part in lines 297-301,

which are as follows:

**Lines 297-301:** Next, computational performance was compared for the Fortran version of HADVPPM on the Intel Xeon E5-2682 v4 CPU and domestic CPU processor A, the CUDA version of GPU-HADVPPM on the NVIDIA Tesla K40m and V100 GPU, and the HIP version of GPU-HADVPPM on the domestic GPU-like accelerator A, under the BJ, HN and ZY case.

#### Line 302:

Lists

**Response:** Sorry for this mistake. We have revised this part in lines 302-303, which are as follows:

**Lines 302-303:** Table 5 lists the elapsed time and speedup of the different versions of HADVPPM on the CPU processors and GPU accelerators for BJ, HN, and ZY cases.

## Lines 318-321:

table 5 might be more informative for the reader in the form of a bar chart.

If I understand this correctly, speed up is computed relative to the elapsed time of the domestic CPU processor A times. Please state this explicitly. Please also state explicitly whether the runs on the CPU (both with the Chinese CPU and the Intel CPUs) are using OpenMP or serial.

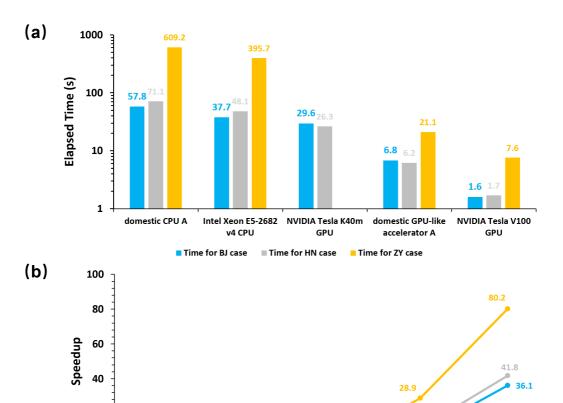

Response: Thanks for the constructive suggestion. We have converted Table 5 into bar and line charts, and the specific form is shown in Figure 5. When evaluating the computational efficiency on different hardware platforms, the elapsed time of advection module launched two CPU processes on the domestic CPU processor A is taken as the benchmark, that is, the speedup is 1.0x. The runtime of the advection module on Intel CPU processor and different GPU accelerators is compared with the baseline to obtain the speedup. As mentioned above, when two CPU processes are launched to run CAMx, only the P1 process is involved in the computing, and the P0 process is mainly responsible for data input/output and communication. We have revised this part in lines 295-321, which are as follows:

Lines 295-321: As described in Sect. 4.2, we validate the 48 hours simulation results outputted by the Fortran, CUDA, and HIP versions of CAMx. Next, computational performance was compared for the Fortran version of HADVPPM on the Intel Xeon E5-2682 v4 CPU and domestic CPU processor A, the CUDA version of GPU-HADVPPM on the NVIDIA Tesla K40m and V100 GPU, and the HIP version of GPU-HADVPPM on the domestic GPU-like accelerator A, under the BJ, HN and ZY case. The simulation time in this section is 1 hour unless otherwise specified. When evaluating the computational efficiency on different hardware platforms, the elapsed time of advection module launched two CPU processes on the domestic CPU processor A is taken as the benchmark, that is, the speedup is 1.0x. The runtime of the advection module on Intel CPU processor

and different GPU accelerators is compared with the baseline to obtain the speedup. As mentioned above, when two CPU processes are launched to run CAMx, only the P1 process is involved in the computing, and the P0 process is mainly responsible for data input/output and communication.

Figure 5(a) and (b) shows the elapsed time and speedup of the different versions of HADVPPM on the CPU processors and GPU accelerators for BJ, HN, and ZY cases, respectively. The results show that using CUDA and HIP technology to port HADVPPM from CPU to GPU can significantly improve its computational efficiency. For example, the elapsed time of the advection module on the domestic processor A is 609.2 seconds under the ZY case. After it is ported to the domestic GPU accelerator and NVIDIA V100 GPU, it only takes 21.1 seconds and 7.6 seconds to complete the computing, and the speedups are 28.9x and 80.2x, respectively. The ZY case had the largest number of grids in the three cases and exceeded the memory of a single NVIDIA Tesla K40m GPU accelerator, so it was not possible to test its elapsed time on it. Moreover, the optimization of thread and block co-indexing is used to simultaneously compute the grid point in the horizontal direction (Cao et al., 2023). Therefore, it can be seen from Figure 5(b) that the larger the computing scale, the more obvious the acceleration, which indicates that GPU is more suitable for super-large scale parallel computing, and provides technical support for accurate and fast simulation of ultra-high-resolution air quality at the meter level in the future.

Intel Xeon E5-2682 v4 NVIDIA Tesla K40m

Speedup for HN case

domestic GPU-like

accelerator A

Speedup for ZY case

**NVIDIA Tesla V100**

20

0

domestic CPU A

Speedup for BJ case

Figure 5. The elapsed time (a) and speedup (b) of the Fortran version of HADVPPM on the Intel Xeon E5-2682 v4 CPU and the domestic CPU processor A, the CUDA version of GPU-HADVPPM on the NVIDIA Tesla K40m GPU, NVIDIA Tesla V100 GPU, and the HIP version of GPU-HADVPPM on the domestic GPU-like accelerator A for BJ, HN, and ZY case. The unit of elapsed time is in seconds (s).

## Lines 307-313:

I think this information is redundant to Table 5. I would suggest to remove it from the text.

It seems the point you intend to highlight is that the speed up is larger for the larger case. I would suggest to write a sentence specifically on that. The readers can check the numbers in the table.

**Response:** Thanks for the constructive suggestion. We have removed the redundant information from the text, and revised this part in **lines 302-317**, which are as follows:

Lines 302-317: Figure 5(a) and (b) shows the elapsed time and speedup of the different versions of HADVPPM on the CPU processors and GPU accelerators for BJ, HN, and ZY cases, respectively. The results show that using CUDA and HIP technology to port HADVPPM from CPU to GPU can significantly improve its computational efficiency. For example, the elapsed time of the advection module on the domestic processor A is 609.2 seconds under the ZY case. After it is ported to the domestic GPU accelerator and NVIDIA V100 GPU, it only takes 21.1 seconds and 7.6 seconds to complete the computing, and the speedups are 28.9x and 80.2x, respectively. The ZY case had the largest number of grids in the three cases and exceeded the memory of a single NVIDIA Tesla K40m GPU accelerator, so it was not possible to test its elapsed time on it. Moreover, the optimization of thread and block co-indexing is used to simultaneously compute the grid point in the horizontal direction (Cao et al., 2023). Therefore, it can be seen from Figure 5(b) that the larger the computing scale, the more obvious the acceleration, which indicates that GPU is more suitable for super-large scale parallel computing, and provides technical support for accurate and fast simulation of ultrahigh-resolution air quality at the meter level in the future.

## Line 326:

Missing (

**Response:** Sorry for this mistake. We have revised this part in **lines 324-326**, which are as follows:

**Lines 324-326:** However, the communication bandwidth of data transfer between the CPU and GPU is one of the most significant factors that restrict the performance of numerical model on the heterogeneous cluster (Mielikainen et al., 2012; Mielikainen et al., 2013; Huang et al., 2013).

## Line 327:

study, explore, illustrate?

**Response:** Sorry for not being able to explain it clearly. We have revised this part in **lines 326-329**, which are as follows:

**Lines 326-329:** To illustrate the significant impact of CPU-GPU data transfer efficiency, the computational performance of GPU-HADVPPM with and without data transfer time for the BJ case is tested on the "Songshan" supercomputer and "Taiyuan" computing platform with the same DTK version 23.04 software environment.

## Line 322:

Coupled?

**Response:** Sorry for not being able to explain it clearly. We have revised this part in **lines 322-324**, which are as follows:

**Lines 322-324:** In the above experiments to test the computational performance of GPU-HADVPPM on NVIDIA GPU and domestic GPU-like accelerator, the data transfer time between CPU and GPU was not considered.

## Line 327:

Coupled?

**Response:** Sorry for not being able to explain it clearly. We have revised this part in **lines 326-329**, which are as follows:

**Lines 326-329:** To illustrate the significant impact of CPU-GPU data transfer efficiency, the computational performance of GPU-HADVPPM with and without data transfer time for the BJ case is tested on the "Songshan" supercomputer and "Taiyuan" computing platform with the same DTK version 23.04 software environment.

### Lines 329-331:

this means the time that the accelerators are actually computing? Please call it something like kernel execution time or something along these lines. The other time is of course simply the total elapsed time or total runtime.

**Response:** Sorry for not being able to explain it clearly. We refer to the execution time of GPU-HADVPPM program on GPU kernel as kernel execution time, and the time of GPU-HADVPPM running on GPU as total runtime, which contains two parts, namely, kernel execution time and data transfer time between CPU-GPU. We have revised this part in **lines 329-331**, which are as follows:

Lines 329-331: For convenience of description, we refer to the execution time of GPU-HADVPPM

program on GPU kernel as kernel execution time, and the time of GPU-HADVPPM running on GPU as total runtime, which contains two parts, namely, kernel execution time and data transfer time between CPU-GPU. After testing, the kernel execution time and total running time of GPU-HADVPPM4HIP program on domestic GPU-like accelerator A are 6.8 seconds and 93.1 seconds, respectively, which means that only 7.3% of the time is spent on GPU computing, and the rest is spent on data transfer.

## Lines 332-333:

This is really very inefficient.

Response: By comparing the kernel execution time and total running time of GPU-HADVPPM4HIP on the domestic accelerator, it can be seen that the data transfer efficiency between CPU-GPU is really inefficient, which seriously restricts the computational performance of numerical models in heterogeneous clusters. On the one hand, improving the data transfer bandwidth between CPU-GPU can improve the computational efficiency of the model in heterogeneous clusters. On the other hand, the optimization measures can be implemented to improve the data transfer efficiency between CPU-GPU. For example, (1) Asynchronous data transfer is used to reduce the communication latency between CPU and GPU. Computation and data transfer are performed simultaneously to hide communication overhead; (2) Currently, some advanced GPU architectures support a unified memory architecture, so that the CPU and GPU can share the same memory space and avoid frequent data transfers. This reduces the overhead of data transfer and improves data transfer efficiency; (3) Cao et al. (2023) adopted communication optimization measures to reduce the communication frequency in one time integration step to one, but there is still the problem of high communication frequency in the whole simulation. In the future, we will consider porting other hotspots of CAMx model, or even the whole integral module except I/O, to GPU-like accelerators for increasing the proportion of code on the GPU and reduce the frequency of CPU-GPU communication. We have revised this part in lines 335-349, which are as follows:

Lines 335-349: By comparing the kernel execution time and total running time of GPU-HADVPPM4HIP on the domestic accelerator, it can be seen that the data transfer efficiency between CPU-GPU is really inefficient, which seriously restricts the computational performance of numerical models in heterogeneous clusters. On the one hand, improving the data transfer bandwidth between CPU-GPU can improve the computational efficiency of the model in heterogeneous clusters. On the other hand, the optimization measures can be implemented to improve the data transfer efficiency between CPU-GPU. For example, (1) Asynchronous data transfer is used to reduce the communication latency between CPU and GPU. Computation and data transfer are performed simultaneously to hide communication overhead; (2) Currently, some advanced GPU architectures support a unified memory architecture, so that the CPU and GPU can

share the same memory space and avoid frequent data transfers. This reduces the overhead of data transfer and improves data transfer efficiency; (3) Cao et al. (2023) adopted communication optimization measures to reduce the communication frequency in one time integration step to one, but there is still the problem of high communication frequency in the whole simulation. In the future, we will consider porting other hotspots of CAMx model, or even the whole integral module except I/O, to GPU-like accelerators for increasing the proportion of code on the GPU and reduce the frequency of CPU-GPU communication.

## Lines 335-337:

how do you propose to do this?

Response: For the problem of inefficiency of data transfer between CPU-GPU, we plan to carry out performance optimization in the following three aspects in the future. (1) Asynchronous data transfer is used to reduce the communication latency between CPU and GPU. Computation and data transfer are performed simultaneously to hide communication overhead; (2) Currently, some advanced GPU architectures support a unified memory architecture, so that the CPU and GPU can share the same memory space and avoid frequent data transfers. This reduces the overhead of data transfer and improves data transfer efficiency; (3) Cao et al. (2023) adopted communication optimization measures to reduce the communication frequency in one time integration step to one, but there is still the problem of high communication frequency in the whole simulation. In the future, we will consider porting other hotspots of CAMx model, or even the whole integral module except I/O, to GPU-like accelerators for increasing the proportion of code on the GPU and reduce the frequency of CPU-GPU communication. We have revised this part in lines 335-349, which are as follows:

Lines 335-349: By comparing the kernel execution time and total running time of GPU-HADVPPM4HIP on the domestic accelerator, it can be seen that the data transfer efficiency between CPU-GPU is really inefficient, which seriously restricts the computational performance of numerical models in heterogeneous clusters. On the one hand, improving the data transfer bandwidth between CPU-GPU can improve the computational efficiency of the model in heterogeneous clusters. On the other hand, the optimization measures can be implemented to improve the data transfer efficiency between CPU-GPU. For example, (1) Asynchronous data transfer is used to reduce the communication latency between CPU and GPU. Computation and data transfer are performed simultaneously to hide communication overhead; (2) Currently, some advanced GPU architectures support a unified memory architecture, so that the CPU and GPU can share the same memory space and avoid frequent data transfers. This reduces the overhead of data transfer and improves data transfer efficiency; (3) Cao et al. (2023) adopted communication optimization measures to reduce the communication frequency in one time integration step to one, but there is still the problem of high communication frequency in the whole simulation. In the future,